## International Journal of Nanoelectronics and Materials

- IJNeaM -

ISSN 1985-5761 | E-ISSN 2232-1535

# Investigation on Geometrical Effects of FinFET Electronic Device Properties Using TCAD Simulations and Taguchi Optimization

Ahmad Syaiful Othman<sup>1,a</sup>, Sabrina Reezal<sup>2,a</sup>, Rafidah Rosman<sup>3,a</sup>, Maizan Muhamad<sup>4,a</sup>, Hanim Hussin<sup>5,a\*</sup>, Nurul Ezaila Alias<sup>6,b</sup>, Yasmin Abdul Wahab<sup>7,c</sup>, Md Fokhrul Islam<sup>8,d</sup>

- alntegrated Microelectronic, System and Applications, Faculty of Electrical Engineering, Universiti Teknologi MARA, 40450, Shah Alam,

- <sup>b</sup>Faculty of Electrical Engineering, Universiti Teknologi Malaysia, 81310 Johor Bahru, Malaysia

- Center of Printable Electronics, Research Management Center, University of Malaya, 50603, Kuala Lumpur, Malaysia

- <sup>d</sup>Department of Electrical and Electronic Engineering, Islamic University of Technology, Gazipur, Bangladesh

- \*hanimh@uitm.edu.my

Received XXX 2023, Revised XXX 2023, Accepted XXX 2023

#### ABSTRACT

To ensure optimal operating conditions and performance, transistor dimension parameters must be determined accurately. This work investigates the Taguchi approach for device parameter optimization in a 7nm Silicon FinFET, employing design of experiments (DOE) methodologies to improve device performance and efficiency. In this work, the geometric scaling that affect FinFET performance, with an emphasis on the ratio of on-state current (IOFP), threshold voltage (VTH), subthreshold swing (SS) and drain induced barrier lowering (DIBL) are investigated. The Taguchi approach is used to optimize the FinFET model, resulting in improved performance. Furthermore, investigation on the impact of optimized FinFETs on logic circuit performance, notably delay and power characteristics. Moreover, the Silvaco TCAD Simulator is used as the medium of simulation and analysis. The Taguchi method was implemented to determine the most appropriate combination of factors for robust device performance using orthogonal arrays, and signal-to-noise (SN) ratio as the quality characteristic of choices. The factors involved in the design of experiments include the length (LG) and height (HFIN) of the fin as well as the width (WFIN) of the fin at the top region. Using Taguchi's robust performance signal-to-noise ratio, the combination of parameters was obtained for the ION/IOFF ratio, VTH, DIBL, and SS. The VTH value is 0.7461V for FinFET with LG, WFIN, HFIN being 13 nm, 7 nm, and 35 nm, respectively. The current ratio of 262.072 and SS of 69.4 mV/dec obtained from FinFET when LG is 13 nm, WFIN is 5 nm, and HFIN is 40 nm. For the optimum DIBL, which is 232 mV/V, is gained when the FinFET has LG, WFIN, and HFIN 10 nm, 10 nm, and 35 nm, respectively. The analysis confirms that dimension optimization can significantly enhance FinFET performance. The use of the Taguchi method proved effective in identifying the optimal parameter combinations, and the subsequent application to logic circuits for the development of low-power FinFETs.

$\textbf{Keywords:} \ design \ of \ experiments \ (DoE), SiO2, off-current \ (IOFF), on-current \ (ION), SN \ ratio, Taguchi \ method, TCAD \ simulation, fin \ length \ (LG), fin \ height \ (HFIN), fin \ width \ (WFIN) \ threshold \ voltage \ (VTH), subthreshold \ swing \ (SS), \ drain \ induced \ barrier \ lowering \ (DIBL)$

### 1. INTRODUCTION

FinFET is a potential successor for CMOS device architectures in the nanometer range. It provides great control over SCEs (short channel effects) such as leakage current, DIBL, and perfect sub-threshold slope. Because 7nm FinFETs have less critical dimensions, they contribute to improved performance by providing significant channel control. According to ITRS, FinFET will propel technology from the sub-nanometer range up to the 5nm node. [1], [2]. Various manufacturers, including Samsung, Global Foundry, and Intel, are working at the 14 nm node. Broadwell-y, an Intel Core M processor, is built on 14nm technology. Intel is primarily focused on optimizing FinFETs by increasing HFIN. FinFET VTH properties are determined by HFIN and WFIN. In this work, the design optimization of FinFET performance is focusing on device dimension consisting of channel length, finger width and finger height. The electrical characteristics of a 7nm FinFET includes VTH, ION/IOFF ratio, SS, and DIBL are optimized using the Taguchi method and design of experiments. To understand the performances characteristics, the effects of varying fin LG, WFIN, and HFIN on VTH, ION/IOFF ratio, SS, and DIBL are studied

### 2. LITERATURE REVIEW

The short channel effect occurs when the conductive channel length of a FinFET is less than 20 nanometers, or even ten nanometers. The impacts of decreasing channel length include lower threshold voltage, and lower leakage-induced barrier. Shorter gate lengths in FinFETs lead to less channel control capacity. This makes it difficult for the gate voltage to push off the channel, resulting in sub-threshold leaking. The short channel impact is more likely to occur [3]. Generally, LG should be more than or equal to Fin Width for better DIBL control and a current ratio. DIBL is a unique method for assessing short-channel effects in electronics. DIBL tends to increase when LG scales down, with its LG being determined by the scaling length of the devices. [4]. The FinFET structure was created to address MOSFET scaling issues, which limited devices scalability. High

1

leakage current in short channel transistors reduces switching performance by lowering the ION/IOFF ratio. ION and IOFF are key electrical characteristics used to evaluate device performance, especially switching speed and standby time [5]. To obtain reliable switching performance, Ion should be higher and IOFF as close to zero as possible, resulting in a high ION/IOFF ratio. Off-state leakage current is also reduced by technology. However, the older MOSFETs have surpassed their key scalability and performance limits. One major downside of this device is its extremely low threshold potential, which allows for quick device startup [6] [7]. The reduction of the potential barrier eventually allows electron flow between the source and the drain, even if the gate-to-source voltage is lower than the threshold voltage [8]. In FinFETs, the VTH can be reduced to improve device performance while also reducing leakage current significantly [9]. The SS increases significantly when the gate length is shortened. The SS increases when the drainto-source voltage increases. It is caused by the enhancement of subthreshold current due to lowering the potential barrier height by drain effect. [10] Conclude that it aims to optimize the electrical characteristics of a 7nm FinFET using the Taguchi method and design of experiments. Moreover, it investigates the effects of varying fin LG, WFIN, and HFIN on VTH, ION/IOFF ratio, SS, and DIBL.

#### 3. METHODOLOGY

Figure 1 shows the flowchart to represent project's technique. First, it will design the FinFET technology behaves based on its factors that will be used. To progress technology, this involves evaluating the device's attributes, capabilities, performance, and other areas. The TCAD simulation will optimize and make use of all the study data that has been gathered. We will assess the performance and examine the effects of lowering the geometric and parametric parameters of the FinFET based on the results of the simulation. With the aid of this data, the settings that provide the device with its best performance characteristics can be found

### 3.1. Silvaco TCAD

The research was carried out using simulation in the SILVACO TCAD software. The source and drain lengths (LS/LD) and gate lengths (LG) in nanometers are the parameters utilized in the FinFETs. WFin is the width and HFin is the height of the vertical silicon fin. The source and drain areas are doped with 1.20×10 cm<sup>-3</sup> donor concentration, whereas the channel is evenly doped with 1.45×10 cm<sup>-3</sup> acceptor dopant. Figure 1 shows the flowchart of Silvaco TCAD simulation. Figure 2 shows the 3D structure of the FinFETs used in this work. The simulation used 2D Schrodinger-Poisson model, and the quantization inside the channel is nearly 2-dimensional. Equation 1 and 2 are used in the simulation to extract subthreshold swing and the DIBL respectively [5].

$$SS = \frac{dV_{GS}}{d(\log_{10}I_{DS})} \tag{1}$$

$$DIBL = \frac{\Delta V_{TH}}{\Delta V_{DS}} \tag{2}$$

Figure 1. Flowchart of Silvaco TCAD simulation

Figure 2. 3D structure of the FinFETs from the SILVACO TCAD Simulation.

#### 3.2. Taguchi Method

The Taguchi method is one of several statistical strategies that are highly beneficial to answer complex and difficult problems with the fewest variables and fewer tests in numerous domains [11]. The Taguchi approach aims to find the parameters or factors that have a substantial impact on product performance. Hence, it employs orthogonal arrays to systematically vary simulation parameters and analyze their influence on target performance metrics. In this study, the Taguchi method was used to optimize the FinFET device geometry by exploring the impact of three key factors such as channel length (Lg), fin width (Wfin), and fin height (Hfin) on threshold voltage (Vth), Ion/Ioff ratio, subthreshold swing (SS), and drain-induced barrier lowering (DIBL).

To study the effects of each parameter variation. Table 1 summarizes the three-level design of experiments, with each factor assigned levels 0, 1, and 2. The L27 orthogonal array  $(3^3$  design) was selected to balance design comprehensiveness with computational efficiency. Each simulation scenario corresponds to one combination of parameter levels [12].

#### Table 1. Factors and levels used in the parameters

| I | Symbol | Factors        | Level |    |    |  |  |

|---|--------|----------------|-------|----|----|--|--|

| ı |        |                | 0     | 1  | 2  |  |  |

| Ī | A      | Channel Length | 10    | 13 | 15 |  |  |

| Ī | В      | Fin Width      | 5     | 7  | 10 |  |  |

| Ī | С      | Fin Height     | 30    | 35 | 40 |  |  |

Parameters that have been varied are shown in Table 1 which are LG, WFIN, and HFIN which were assigned as A, B and C respectively. These factors are set at three levels each, where '0' defines the least value while '2' defines the biggest. Meanwhile, the responses or the desired output measures are the VTH, ION/IOFF, SS, and DIBL using the smaller the better (STB), the larger the better (LTB) and the nominal the better (NTB) respectively.

The three-level standard orthogonal arrays used in this work is L27(33) [12]. In this work, the factors level is varied by previous work, where it researches to optimize the FinFET [13] [14]. In addition, all the design parameters and electrical characteristics of the structure were calibrated as per the guidelines of ITRS.

### 3.3. Synopsis Hspice

FinFET library from Predictive Technology Models (PTM) is used in this work. These predictive files were chosen because they are compatible with the HSpice simulator and can handle a wide range of process changes. Following that, a simulation will be run using data from the Taguchi method, with the primary goal of optimizing both delay and power consumption in the circuit. Inverter circuits are used in this work to study delay and power consumption. Figure 3 shows the flowchart of simulation on Hspice.

Figure 3. Flowchart of simulation on Hspice

#### 4. RESULTS AND DISCUSSION

In this section, the effect of variation in WFIN, LG, and HFIN on the electrical characteristics of devices has been discussed. The objective of this paper is to optimize VTH, ION/IOFF, SS, and DIBL use the DOE based on the WFIN, LG, and HFIN. The VTH, ION/IOFF, SS, and DIBL performances of the FinFET statistically using the Taguchi method. Should the device aim for higher ION/IOFF ratio, the LTB characteristic is applied to perform the DOE. In terms of IOFF performance, the device requires low subthreshold leakage thus using the STB characteristics. Meanwhile in terms of VTH, the LTB characteristic is applied to perform the experiments.

## 4.1. Effects of physical parameters variation on $V_{\text{TH}},\,I_{\text{ON}}/I_{\text{OFF}}$ RATIO, SS and DIBL

For FinFET devices, the threshold voltages may be adjusted by imposing the various gate materials, whose work function may play crucial roles in controlling the values of threshold voltages. The VTH is nominal at all points, which makes all the parameters combination does not make too much difference. The threshold voltage (Vth) was extracted using the constant current method, defined as the gate voltage (Vg) at which the drain current (Id) reaches  $10^{\Lambda}$ -7 A/ $\mu$ m, under a drain bias of Vds = 0.7 V. This method ensures consistent comparison across device geometries.

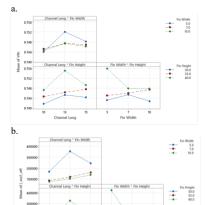

The proposed 7nm device has a higher ION/IOFF ratio that is satisfactory for any electrical device [15]. Having higher HFIN can give a higher ION/IOFF ratio. Hence in terms of ION/IOFF ratio proposed device have higher value, so it performs much better from the older MOSFET. From the existing technology it is found that the proposed 7nm device operates with minimal leakage and drive current along with a better ION/IOFF ratio. Furthermore, when it indicates that as the channel length is decreased, the SS can be the better immunity to SCEs. Figure 4(C) shows the subthreshold swing roll-up versus the channel length for different fin width. In comparison, the smaller width is 5nm, the more subthreshold swing can roll-up. The main reason is that the width can induce a shorter scaling length, which hence results in less subthreshold behavior degradation than the wider one [16]. As the LG is narrowed down to 10nm, the DIBL effect is more distinct. However, the trend of DIBL in short-channel devices with channel widths is clearly increased, but not consistent. This phenomenon is perhaps that the etch bias is not easily controlled. As the channel width is increased, the DIBL is increased due to the better uniformity of threshold voltage implantation. When the channel length is increased, the DIBL value is also increased. The cause is like the statement at the DIBL discussion. The internal electrical filed due to the LG brings down the impact of punch-through effect [17].

**Commented [sr1]:** Tanya Dr, perlu tambah formula dan explain mcm STB utk output apa begitu NTB, LTB.

Author's Name, et al. / Title of the paper

Figure 4. Effect of a) VTH, b) ION/IOFF, c) SS, and d) DIBL on different  $L_{G},\,W_{FIN},\,H_{FIN}$

## $4.2.\ Optimization\ of\ VTH,\ ION/IOFF\ RATIO,\ SS\ and\ DIBL.$

The effects of geometry scaling resulting in VTH are presented in figure 4(a), with the optimization VTH is getting smaller. The combination of geometry shows that LG is 13nm, WFIN is 7nm, and HFIN is 35nm. The VTH is 0.7461V did cause of the source-drain regions are very close with each other to the point that the current charge being controlled by gate is reduced. Some of the charges allow flow between the source and the drain in the channel, hence lowering the VTH. However, further reduction of the parameter shown decreasing unstable of device and probably implying that SCEs is getting worse. Moreover, figure 4(b) shows the SNR of the three factors on ION/IOFF characteristics. As the device shrinks, the ION/IOFF shows huge improvements with the combination that gained from the Taguchi, the ratios mostly up to 106. The combination to get the optimum ratio are LG is 13nm, WFIN is 5nm, and HFIN is 40nm. The rising ION/IOFF drops drastically at Lg around 15 nm indicating the relative increase in IOFF is substantial compared to the small increase of ION. This observation is essential since it demonstrates how combinations parameter can affect the performance of FinFET. The effect of reducing parameters has given the output of higher ratio of ION/IOFF. When the ratio increases, it shows that the device is becoming faster and reducing the leakage current. The figure and table below show the effect of each factor that relates to the current ratio. It represents the optimize combination based on the SNR. Then, from figure 4(c), it can be observed that the SS is better when the parameters LG is 13nm, WFIN is 5nm, and HFIN is 40nm. It gives the SS result as 69.4mV/dec which happens to give

low power, because of lower SS reduce the power. Fundamentally reducing the voltage to achieve desired on-off switch [18]. The obtained of SS in this analysis provides a rough qualitative sign of the reducing of short channel effect (SCE) of a short transistor. Lastly, as shown in figure 4(d) DIBL results in lowering of barrier height of a the FinFET due to drain voltage. DIBL must be less so that device can go to off condition. The higher the value, the more chance a device failed to go in off condition. DIBL on FinFET depends on Fin width. The channel length must be greater or be the same as Fin width to effectively suppress DIBL [19]. Based on the result it shows that the combination of parameters  $\mathbb{L}G$  is 10nm, WFIN is 10nm, and HFIN is 35nm have given the effective DIBL which is around 232 mV/V.

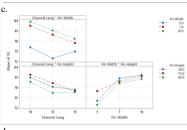

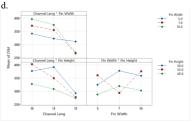

**Figure 5.** average SNR against factor level for a)VTH b)ION/IOFF c)SS d)DIBL on channel length, fin width and fin height

## 4.3. Pareto Analysis of Variance (ANOVA)

To validate the results, the contribution of each geometrical parameter to each device's performance was further investigated by applying ANOVA. Figure 6 the Pareto diagram of designs aiming

**Commented [sr2]:** Tanya Dr, tentang Wfin pada 35 bukan sepatutnya nilai adalah >364?

Commented [sr3]: 1.Ref: N.A.F Othman

2. study mcm mana pareto diagram diterangkan, cara relate value2 / bacaan dari graph

International Journal of Nanoelectronics and Materials (IJNeaM) Volume XX, No. X, Month 20XX [1-4]

for an efficient VTH, ION/IOFF, SS, and DIBL performances, for the FinFET, respectively. It is observed that interaction for all parameters, in all characteristics. The interaction is classified as (A×B), (A×C), and (B×C). The NTB analysis was chosen for the optimal VTH, which is justified. Following the next characteristic, which is the current ratio, the interaction demonstrates that the LTB analysis produced the same result as Taguchi. Furthermore, the SS and DIBL determined by LTB analysis have been supported by the interaction depicted in the figure 5(a) and 5(d). Following the result gain, it approves that every combination gives the optimum result between the interactions.

Figure 6. Average SNR against factor level for a) VTH b)  $ION/IOFF\ c)$  SS d) DIBL on channel length, fin width and fin height.

## 4.4. Implementation on inverter performance for circuit level optimization.

Table 2 demonstrates that the power of this work is improved with this combination parameter at the nanoscale as compared to others. The VTH optimization 33 combinations achieved a 46.9% improvement in faster delays and a 93.8% reduction in power consumption compared to the default configuration. These improvements are due to the low voltage used to reduce power consumption. It has been established that the smaller the device, the lower the voltage that can be employed for low-power applications. The delay can be compared between the default settings, and it is observed that the delay is improved in this work.

Table 2. Power and delay for each optimization combination.

| Type        | Delay     | Power       |

|-------------|-----------|-------------|

| This Work   | 1.01E-08  | 6.13E-12    |

| Default     | 1.900E-08 | 9.833E-11   |

| Paper 1[20] | -         | 3.989E-9    |

| Paper 2[21] | -         | 2.807383E-9 |

#### 5. CONCLUSION

In this study, the influence of geometric scaling and process parameters on the performance of FinFETs, with a specific focus on key performance indicators such VTH, current ratio, SS and DIBL. FinFET performance is considerably improved by lowering geometric dimensions and optimizing process parameters, especially for low-power applications. The findings demonstrate a significant reduction in SCE and a significant improvement in oncurrent while maintaining a low off-current. The VTH, SS, and DIBL measurements also show improved device stability and performance, confirming the efficiency of these parameter changes for achieving low-power, high-performance FinFETs. The Taguchi approach was then used to optimize the FinFET model, with the goal of increasing the current ratio and improving transistor performance while reducing leakage current. With the Taguchi approach, the design space was effectively explored, and an ideal set of parameters was developed. The SNR analysis revealed that the chosen parameter combination is the most effective at meeting the intended performance targets. This optimization procedure not only improved overall performance metrics but also validated the resilience and reliability of the Taguchi method in semiconductor device optimization. Using the optimized FinFET characteristics in a logic circuit, especially an inverter circuit in HSPICE, resulted in considerable gains in circuit performance. The optimized inverter demonstrated lower power consumption and smaller delay, making it ideal for low-power applications.

### ACKNOWLEDGMENTS

This study received financial support from the Fundamental Research Grant Scheme (FRGS: FRGS/1/2024/TK07/UITM/02/18), administered by the Ministry of Higher Education (MOHE). We sincerely appreciate the assistance and collaboration of the Faculty of Electrical Engineering, Universiti Teknologi MARA, in carrying out this work.

Commented [sr4]: Tanya Dr, utk setiap figure 5 kena terangkan value? cuba refer references dari N.A.F Othman mcm mana dia

Commented [sr5]: 1.Identify "default" dari mana 2. mcm mana nak tahu power dan delay ini observed

Commented [sr6R5]: Default dari PTM model

terangkan tentang SNR figures.

#### REFERENCES

- [1] M. L. Lee, E. A. Fitzgerald, M. T. Bulsara, M. T. Currie, and A. Lochtefeld, "Strained Si, SiGe, and Ge channels for high-mobility metal-oxide-semiconductor field-effect transistors," Jan. 01, 2005. doi: 10.1063/1.1819976.

- [2] S. H. Park et al., "Performance comparisons of III-V and strained-Si in planar FETs and nonplanar FinFETs at ultrashort gate length (12 nm)," IEEE Trans Electron Devices, vol. 59, no. 8, pp. 2107–2114, 2012, doi: 10.1109/TED.2012.2198481.

- [3] Amuthavalli G, Gunasundari R, and Palani U, "Investigation on the Impact of Supply Voltage in Subthreshold Leakage Mitigation."

- [4] S. M. Choi et al., "On the universality of drain-induced-barrier-lowering in field-effect transistors," in Technical Digest International Electron Devices Meeting, IEDM, Institute of Electrical and Electronics Engineers Inc., 2022, pp. 831-834. doi: 10.1109/IEDM45625.2022.10019358.

- [5] N. Chowdhury, Q. Xie, and T. Palacios, "Self-Aligned E-Mode GaN p-Channel FinFET with ION > 100 mA/mm and ION/IOFF > 10," IEEE Electron Device Letters, vol. 43, no. 3, pp. 358–361, Mar. 2022, doi: 10.1109/LED.2022.3140281.

- [6] C. J. Sun et al., "Low ge content ultra-thin fin width (5nm) monocrystalline SiGe n-Type FinFET with low off state leakage and high ION/IOFFratio," IEEE Journal of the Electron Devices Society, vol. 8, pp. 1016–1020, 2020, doi: 10.1109/IEDS.2020.3023953.

- [7] R. Kusuma and V. K. H. R. Talari, "Performance analysis of FinFET using gate stack and workfunction engineering in 14nm technology," in 2021 2nd International Conference for Emerging Technology, INCET 2021, Institute of Electrical and Electronics Engineers Inc., May 2021. doi: 10.1109/INCET51464.2021.9456268.

- [8] S. G. Sai, N. Alivelu Manga, and P. C. Sekhar, "Design and Simulation of FinFET based digital circuits for low power applications," in 2020 IEEE International Students' Conference on Electrical, Electronics and Computer Science, SCEECS 2020, Institute of Electrical and Electronics Engineers Inc., Feb. 2020. doi: 10.1109/SCEECS48394.2020.123.

- [9] M. K. Ram, N. Tiwari, D. B. Abdi, and S. Saurabh, "Effect of Drain Induced Barrier Enhancement on Subthreshold Swing and OFF-State Current of Short Channel MOSFETs: A TCAD Study," IEEE Access, vol. 9, pp. 141321–141328, 2021, doi: 10.1109/ACCESS.2021.3119858.

- [10] Q. Nguyen-Gia, M. Kang, J. Jeon, and H. Shin, "Models of Threshold Voltage and Subthreshold Slope for Macaroni Channel MOSFET," IEEE Electron Device Letters, vol. 41, no. 7, pp. 973–976, Jul. 2020, doi: 10.1109/LED.2020.2995642.

- [11] Dalibor. Biolek, Comparison of 2k-Factorial and Taguchi Method for Optimization Approach in 32nm NMOS Device. WSEAS Press, 2013.

- [12] N. A. F. Othman, F. N. N. Azhari, S. F. W. M. Hatta, and N. Soin, "Optimization of 7 nm Strained Germanium FinFET Design Parameters Using Taguchi Method and Pareto Analysis of Variance," ECS Journal of Solid State

- Science and Technology, vol. 7, no. 4, pp. P161–P169, 2018, doi: 10.1149/2.0081804jss.

- [13] A. F. Roslan, F. Salehuddin, A. S. M. Zain, K. E. Kaharudin, and I. Ahmad, "Optimization of 16 nm DG-FinFET using L25 orthogonal array of Taguchi statistical method," Indonesian Journal of Electrical Engineering and Computer Science, vol. 18, no. 3, pp. 1207–1214, 2020, doi: 10.11591/ijeecs.v18.i3.pp1207-1214.

- [14] Abhishek Kumar and Sruti Suvadarsini Singh, Optimizing FinFET Parameters for Minimizing Short Channel Effects. IEEE, 2016. doi: 10.1109/ICCSP.2016.7754396.

- [15] N. A. F. Othman, F. N. N. Azhari, S. F. W. M. Hatta, and N. Soin, The Application of Taguchi Method on the Robust Optimization of p-FinFET Device Parameters. IEEE, 2016. doi: 10.1109/SMELEC.2016.7573611.

- [16] Y. C. Eng et al., "Importance of  $\Delta$  VDIBLSS/(Ion /Ioff) in evaluating the performance of n-channel bulk FinFET devices," IEEE Journal of the Electron Devices Society, vol. 6, no. 1, pp. 207–213, Jan. 2018, doi: 10.1109/JEDS.2018.2789922.

- [17] T. K. Chiang, "A New Short-Channel-Effect-Degraded Subthreshold Behavior Model for Double-Fin Multichannel FETs (DFMcFETs)," IEEE Trans Nanotechnol, vol. 16, no. 1, pp. 16–22, Jan. 2017, doi: 10.1109/TNANO.2016.2622246.

- [18] Shara Mathew, Nithin, K. N. Bhat, and Rathnamala Rao, Investigations on the effect of Dual Material Gate work function on DIBL and Subthreshold Swing in Junctionless FinFETs. IEEE, 2020. doi:

- 10.1109/CONECCT50063.2020.9198438.

- [19] S. E. Huang, W. X. You, and P. Su, "Mitigating DIBL and Short-Channel Effects for III-V FinFETs with Negative-Capacitance Effects," IEEE Journal of the Electron Devices Society, vol. 10, pp. 65–71, 2022, doi: 10.1109/JEDS.2021.3133453.

- [20] D. Singh and M. Yadav, "Performance Analysis of Junctionless and Inversion Mode Trigate SOI FinFET at 20nm Gate Length," in Proceedings 2022 IEEE International Symposium on Smart Electronic Systems, iSES 2022, Institute of Electrical and Electronics Engineers Inc., 2022, pp. 153–157. doi: 10.1109/iSES54909.2022.00040.

- [21] Z. Zhang et al., "FinFET with Improved Subthreshold Swing and Drain Current Using 3-nm Ferroelectric Hf0.5Zr0.5O2," IEEE Electron Device Letters, vol. 40, no. 3, pp. 367–370, Mar. 2019, doi: 10.1109/LED.2019.2891364.

- [22] X. He et al., Impact of Aggressive Fin Width Scaling on FinFET Device Characteristics. IEEE, 2017. doi: 10.1109/IEDM.2017.8268427.

- [23] V. Mishra and S. Akashe, "Calculation of average power, leakage power, and leakage current of FinFET based 4-bit priority encoder," in International Conference on Advanced Computing and Communication Technologies, ACCT, Institute of Electrical and Electronics Engineers Inc., Apr. 2015, pp. 65–69. doi: 10.1109/ACCT.2015.82.

International Journal of Nanoelectronics and Materials (IJNeaM) Volume XX, No. X, Month 20XX [1-4]